What is arbiter PUF, and how can it be implemented in FPGA?

If two athletes are running on a racing track, and the track length is equal, the referee is unbiased, and the outcome is accurate, then who will reach the end line first? You can make an informed guess if you're familiar with the candidate's previous performance. But what if you don't know this? The outcome is pretty random, right? The variation in the candidate's stamina will determine the outcome. Can we generate random numbers in this race? Let's make a protocol to generate random numbers.

Our Hypothetical Protocol

When the 2nd candidate reaches the end line, she will observe if the 1st candidate has crossed the end line or not. If yes, then he'll say one else zero (let's say it's a response). We can perform it with n groups to generate an n-bit random number. But his is just a random number. To get more numbers, we vary the track length. Again, the variation in track length (let's say it's a challenge) changes the outcome. This hypothetical protocol is how we can generate multiple random numbers. In summary, we'll give a group of athletes a challenge, and they'll provide a random response. Let's explore how we can generate random numbers practically within the circuit.

Arbiter Physically Unclonable Function (APUF)

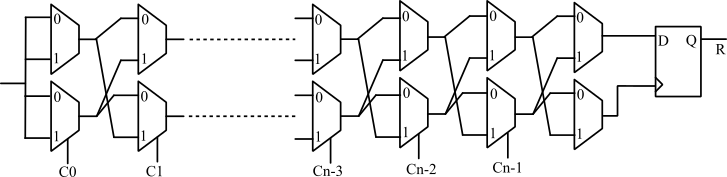

APUF is a delay-based PUF, which means that variations in gate delay and wire delay determine the circuit's response. It is designed using two or more cross-coupled multiplexers, with the output of the last multiplexers connected to the D flip-flop. The select line of the MUX is called a challenge, and the output of the D flip-flop is called a response.

Even though the design utilizes the same MUXs and flip-flops, the gates and wires will be equipped with unavoidable random variations resulting from the manufacturing process after fabrication. Now, we can leverage this variation to get random numbers.

PUF Implementation In FPGA

A simple APUF is implemented in the FPGA and is available in the GitHub repository. The MUX is directly implemented in the LUT, rather than using a Verilog description, to avoid unnecessary minimization of the circuit, which would result in no circuit implementation and, consequently, no output.

Let's See The Results

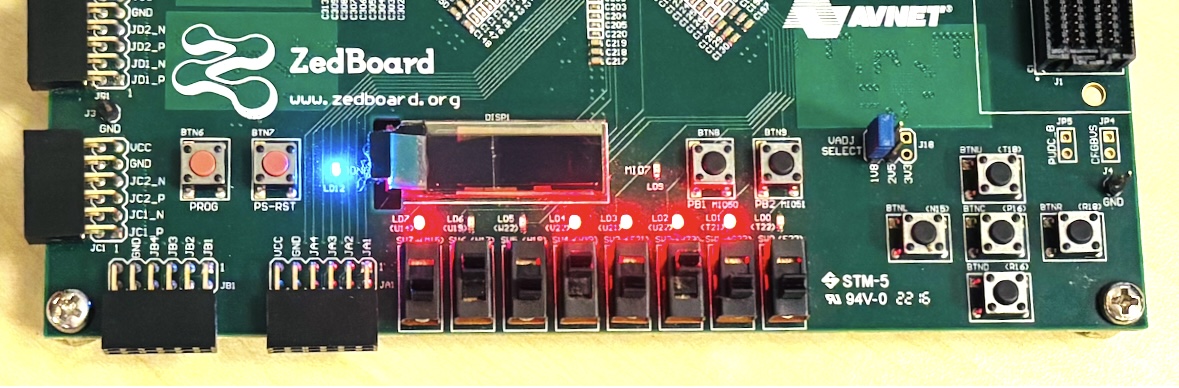

To implement it in your FPGA, change the constraints file. Connect enable signal to a button, challenge to switches, and respond to LEDs. Generate the bitstream, program the FPGA, select a challenge (01010100), and observe the response. If you get a response other than (00000000), comment your response below in the comment section. Let's see if we get random responses for the same challenge. My response is (10011110).