Getting Started With Verilog HDL

Verilog hardware description language or Verilog HDL is a standard language to describe a digital system. We can describe a hardware in a text and then we can generate netlist from the Verilog source file. We can describe any digial system (hardware) in Verilog. When you start learn Verilog, it is very important to learn basics first.

File Extension

Each verilog file has extension of dov v (filename.v)

Comments

Like C/C++, Verilog also has single line and multi-line comment.

- //This is single line comment

- /* This is multi-line comment */

Module

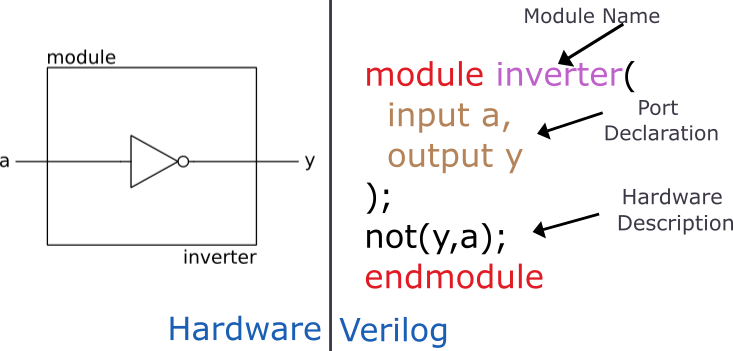

Module is a piece of hardware in Verilog. Each verilog syntax start with module and ends with endmodule

Module name

Each and every module in verilog has uniques name. If your design uses more than one module, then each module should have unique module name.

Port Declaration

As any hardware has input and output ports simillarly, module also has input and output port declaration and it must be declared (Except test bench). Input port is declared using input keyword and output is declared using output keyword.

Hardware description

Hardware is described inside the module and endmodule. The description of the hardware can be any modeling type (structural, data flow or behavioural)

Example

Let us describe a half adder using Verilog HDL.

- Let's create a module

- Let us choose halfadder as module name

- Half adder has two inputs a and b and two outputs sum and carry let's declare it.

- Boolean expression of full adder is $$sum = a \oplus b$$ $$carry = ab$$ let's describe it.

/*

Module : halfadder.v

Created By : circuitfever.com

Create on : 07-11-2022

*/

module

endmodule

/*

Module : halfadder.v

Created By : circuitfever.com

Create on : 07-11-2022

*/

module halfadder

endmodule

/*

Module : halfadder.v

Created By : circuitfever.com

Create on : 07-11-2022

*/

module halfadder(

input a,b,

output sum,carry

);

endmodule

/*

Module : halfadder.v

Created By : circuitfever.com

Create on : 07-11-2022

*/

module halfadder(

input a,b,

output sum,carry

);

xor(sum,a,b); //sum = a exor b

and(carry,a,b); //carry = a and b

endmodule;

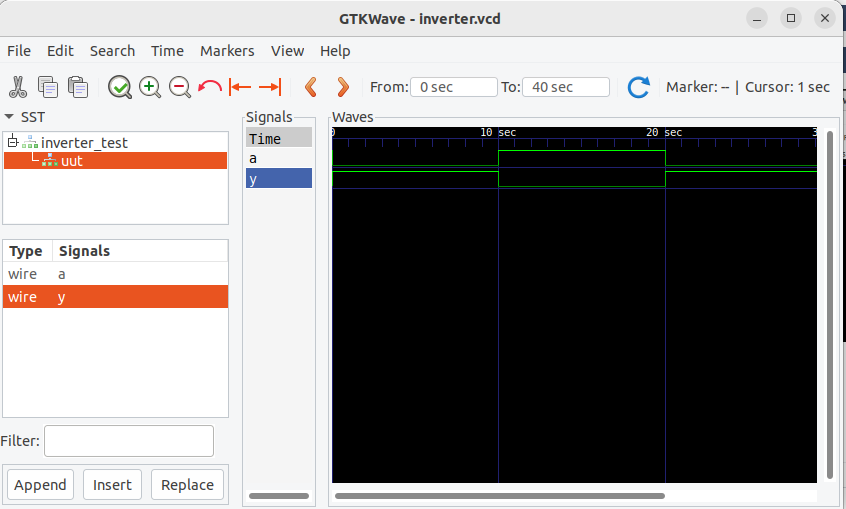

Now we know the very basic of the Verilog HDL and wee need to run this code or hardware description in Verilog synthesis tool. There are open source tool you can use to do synthesis or simulate the above Verilog Code. Below is the link of a tutorial in which how to install tools and simulate Verilog code is discussed.